US009824165B2

# (12) United States Patent

Bantas et al.

# (54) TRANSFORMER SYNTHESIS AND OPTIMIZATION IN INTEGRATED CIRCUIT DESIGN

(71) Applicant: **HELIC S.A.**, Athens (GR)

(72) Inventors: Sotirios Bantas, Athens (GR);

Konstantinos Karouzakis, Athens

(GR); Stefanos Stefanou, Athens (GR);

Apostolos Liapis, Athens (GR); Labros

Kokkalas, Athens (GR); Konstantinos

Nikellis, Athens (GR); Errikos Lourandakis, Athens (GR)

(73) Assignee: Helic S.A., Athens (GR)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 14/710,320

(22) Filed: May 12, 2015

(65) Prior Publication Data

US 2015/0261900 A1 Sep. 17, 2015

# Related U.S. Application Data

- (63) Continuation of application No. 14/045,305, filed on Oct. 3, 2013, now Pat. No. 9,032,355.

- (51) **Int. Cl. G06F 17/50** (2006.01)

H01F 5/00 (2006.01)

- (52) **U.S. CI.**CPC ...... **G06F 17/5009** (2013.01); **G06F 17/5036** (2013.01); **G06F 17/5063** (2013.01); (Continued)

# (10) Patent No.: US 9,824,165 B2

(45) **Date of Patent:**

Nov. 21, 2017

#### (58) Field of Classification Search

# (56) References Cited

#### U.S. PATENT DOCUMENTS

(Continued)

#### OTHER PUBLICATIONS

Yang et. all; "Technique Improving and Its Simulation Analysis on Load Test of Transformer"; Year: 2012; 2012 Asia-Pacific Power and Energy Engineering Conference; pp. 1-4.\* (Continued)

Primary Examiner — Helen Rossoshek (74) Attorney, Agent, or Firm — Shami Messinger PLLC; Khaled Shami

## (57) ABSTRACT

A method for designing a circuit element of an integrated circuit (IC) includes receiving one or more desired characteristics of the circuit element from user input and iteratively determining a design solution through one or more simulations and modifications using a rule-set. The one or more desired characteristics are combined with other preset characteristics of the circuit element or the IC. A first model of the circuit element is defined and simulated to calculate performance. The first and subsequent models are modified by drawing on a rule-set of expert knowledge relating to general dependency of at least one design criterion, such as a physical, geometrical or performance characteristic, with another design criterion.

# 15 Claims, 13 Drawing Sheets

# US 9,824,165 B2

Page 2

| (52)  | CPC <i>G06F 17/5068</i> (2013.01); <i>G06F 2217/02</i> |              |                                                                                                                               | 2003/0182639                 | A1                     | 9/2003      | Bantas                                     |

|-------|--------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------|-------------|--------------------------------------------|

|       | 2217/0                                                 | 08 (2013.    | 06F 2217/06 (2013.01); G06F<br>01); G06F 2217/12 (2013.01);<br>7/16 (2013.01); G06F 2217/78                                   |                              |                        |             | 703/1<br>Rosenberg H04B 3/493<br>379/22.01 |

|       | J                                                      | 2009/0064060 | A1*                                                                                                                           | 3/2009                       | Yoshitomi G06F 17/5063 |             |                                            |

| (58)  | Field of Clas                                          | sificatio    | n Search                                                                                                                      |                              |                        | _,          | 716/100                                    |

| ` ′   | CPC                                                    | 2009/0193370 |                                                                                                                               |                              | Bantas et al.          |             |                                            |

|       |                                                        | 2009/0235208 |                                                                                                                               |                              | Nakayama et al.        |             |                                            |

|       | 2                                                      | 217700, (    | G06F 2217/12; G06F 2217/78;<br>H01F 5/003                                                                                     | 2010/0023896<br>2010/0037189 |                        | 2/2010      | Rastogi et al.                             |

|       | C 1!4!                                                 | 2010/003/189 |                                                                                                                               |                              | Bantas et al.          |             |                                            |

|       | See application                                        | 2010/0088037 |                                                                                                                               |                              | He et al.              |             |                                            |

| (= c) |                                                        |              |                                                                                                                               | 2010/01/3033                 |                        |             | Kurs et al.                                |

| (56)  | References Cited                                       |              |                                                                                                                               | 2011/0025435                 |                        |             | Gorbachov                                  |

|       | U.S. PATENT DOCUMENTS                                  |              |                                                                                                                               | 2011/0113401                 |                        |             | Kireev et al.                              |

|       |                                                        |              |                                                                                                                               | 2012/0022713                 | A1                     | 1/2012      | Deaver, Sr. et al.                         |

|       | C 0.2C 20C A                                           | 2/2000       | T                                                                                                                             | 2012/0112531                 | A1                     |             | Kesler et al.                              |

|       | 6,026,286 A<br>6,629,044 B1*                           | 2/2000       |                                                                                                                               | 2012/0239117                 |                        |             | Kesler et al.                              |

|       | 0,029,0 <del>44</del> B1                               | 9/2003       | Papallo, Jr G06F 17/5036<br>324/424                                                                                           | 2012/0242159                 |                        |             | Lou et al.                                 |

|       | 6,816,012 B2                                           | 11/2004      | Aoki et al. 324/424                                                                                                           | 2012/0248981                 |                        |             | Karalis et al.                             |

|       |                                                        |              | Wilson, Jr G06F 17/5036                                                                                                       | 2012/0280765                 | Al*                    | 11/2012     | Kurs B60L 11/182                           |

|       | 0,632,162 D1                                           | 12/2004      | 703/13                                                                                                                        | 2012/0150056                 |                        | 6/2012      | 333/175                                    |

|       | 6,956,944 B1                                           | 10/2005      |                                                                                                                               | 2013/0159956                 |                        |             | Verghese et al.                            |

|       | 7.020,452 B1                                           |              | Kobayashi                                                                                                                     | 2014/0181782<br>2014/0250417 |                        |             | Verghese et al.<br>Bantas et al.           |

|       | 7,243,321 B2                                           |              | Wang et al.                                                                                                                   | 2014/0230417                 | AI                     | 9/2014      | Dantas et al.                              |

|       | 7,425,869 B2                                           |              | Aoki et al.                                                                                                                   |                              |                        |             |                                            |

|       | 7,496,871 B2 2/2009 Suaya et al.                       |              | OTHER PUBLICATIONS                                                                                                            |                              |                        |             |                                            |

|       | 7,539,965 B2                                           |              | Bromberger et al.                                                                                                             |                              |                        |             |                                            |

|       | 8,032,338 B2 * 10/2011 Akselrod G06F 17/50             |              | Chiang et al., "Optimal capacitor placement, replacement and control in large-scale unbalanced distribution systems: modeling |                              |                        |             |                                            |

|       | 703/1                                                  |              |                                                                                                                               |                              |                        |             |                                            |

|       | 8,108,163 B2                                           |              | Kashiwakura                                                                                                                   | _                            |                        |             | ystems, IEEE Transactions on: vol.         |

|       | 8,181,140 B2                                           |              | Kireev et al.                                                                                                                 |                              |                        | *           | 995, pp. 356-362.                          |

|       | 8,250,506 B2                                           |              | Bantas et al.                                                                                                                 | 10, 133uc 1. 1 ub            | neallo                 | 11 1041. 13 | 775, pp. 556-562.                          |

|       | 8,667,452 B2                                           |              | Verghese et al.                                                                                                               | * aited by ava               |                        |             |                                            |

|       | 8,769,447 B2                                           | //2014       | Bantas et al.                                                                                                                 | * cited by exa               | mmer                   |             |                                            |

<sup>\*</sup> cited by examiner

FIG. 1

FIG. 3

FIG. 4

FIG. 5

FIG. 6A

FIG. 6B

FIG. 7A

FIG. 7B

FIG. 84

FIG. 8B

FIG. 94

FIG. 9B

# TRANSFORMER SYNTHESIS AND **OPTIMIZATION IN INTEGRATED CIRCUIT** DESIGN

# CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a continuation application of U.S. Pat. No. 9,032,355 titled "Integrated Transformer Synthesis and Optimization, issued May 12, 2015, the entire disclosure of 10 which is incorporated herein by reference in its entirety.

## FIELD OF THE INVENTION

The invention relates to the field of Electronic Design 15 Automation (EDA) software for designing inductors, transformers and related circuits particularly for integrated circuits (ICs).

#### BACKGROUND

In electrical and electronic circuit engineering, a transformer is a versatile and ubiquitous component that accomplishes impedance level transformation between its primary providing direct current (DC) isolation between the primary and secondary windings. These properties are useful today in the field of IC design, and especially for radio frequency (RF) IC design, because inductive components such as spiral coils functioning as primary and secondary windings can be 30 fabricated with good performance characteristics using known semiconductor fabrication techniques.

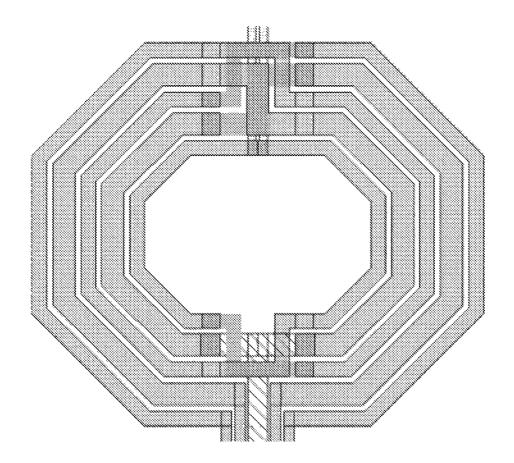

FIG. 1 illustrates an example geometry of a transformer 100 integrated on an IC. An integrated spiral transformer can be employed to transform impedance levels between differ- 35 ent parts of an IC, convert signals from balanced (differential) to single-ended format, or interface chip circuitry to off-chip devices, circuits or fixtures. For instance, an integrated transformer can be employed to interface low impedance (e.g. few ohms) output of an integrated complementary 40 metal oxide silicon (CMOS) power amplifier (PA) through the output pad of the IC and to an external 50-ohm system. Some of these applications are described in detail, for example, in the book "RF Microelectronics" by Behzad Razavi.

What is needed then are methods and systems for improving and/or simplifying the design of components such as integrated spiral transformers for use in ICs fabricated using modern semiconductor fabrication techniques that take into account the different functionality of the designed-for trans- 50 former. formers and the interaction of such transformers with other components of an IC.

#### **SUMMARY**

Embodiments of the invention also provide a method of optimizing the design of a transformer or circuit for an integrated circuit. In an embodiment, a method for designing a transformer in an integrated circuit comprises receiving one or more desired characteristics of the transformer from 60 user input and iteratively determining a design solution for the transformer through one or more simulations and modifications using a rule-set. The method combines the one or more desired characteristics with other preset characteristics of the transformer or the integrated circuit. A first model of 65 the transformer is defined with typical load impedances and simulated having the combined characteristics to determine

performance. Results of the simulation are processed to calculate performance with the load impedances specified by the user. The results are further processed to obtain a mathematical model that includes tuning capacitors. The first and subsequent models are modified by drawing on a rule-set of expert knowledge relating to general dependency of at least one design criterion, such as a physical, geometrical or performance characteristic, with another design criterion.

In an embodiment, the method further comprises receiving one or more optimization targets from user input. A constrained optimization problem is solved to determine optimal values of the tuning capacitors based on the one or more desired characteristics and the one or more optimization targets. In an embodiment, the one or more optimization targets include lowest possible insertion loss.

In an embodiment, the method is usable to design a transformer including a plurality of taps connecting the 20 primary coil to either a fixed potential, a signal, or a load. In an embodiment, the transformer includes a plurality of taps connecting the secondary coil to either a fixed potential, a signal, or a load.

In an embodiment, an apparatus for designing a transand secondary windings through magnetic coupling, while 25 former in an integrated circuit, the apparatus comprises a processor and a user interface adapted to allow a user to input one or more desired characteristics of the transformer. The one or more desired characteristics can include load impedances at primary and secondary coils of the transformer, and the processor is configured to determine sufficient optimal characteristics of the transformer to define the transformer for fabrication in the integrated circuit by executing embodiment of methods for designing a transformer in an integrated circuit comprises receiving one or more desired characteristics of the transformer from user input and iteratively determining a design solution for the transformer through one or more simulations and modifications using a rule-set.

## BRIEF DESCRIPTION OF THE DRAWINGS

Embodiments of the invention will now be described, by way of example only, with reference to the accompanying 45 drawings in which:

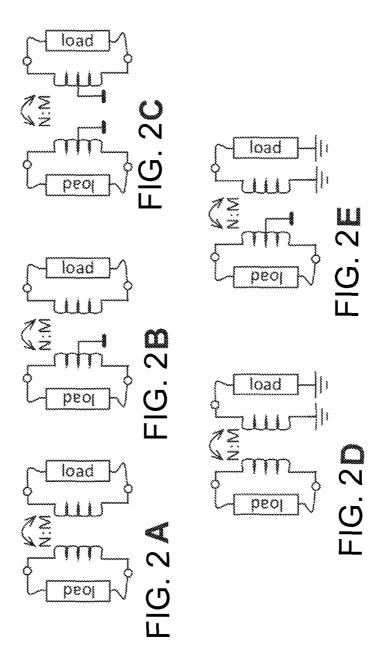

FIG. 1 illustrates a layout of an integrated transformer. FIGS. 2A-2E illustrates various transformer configura-

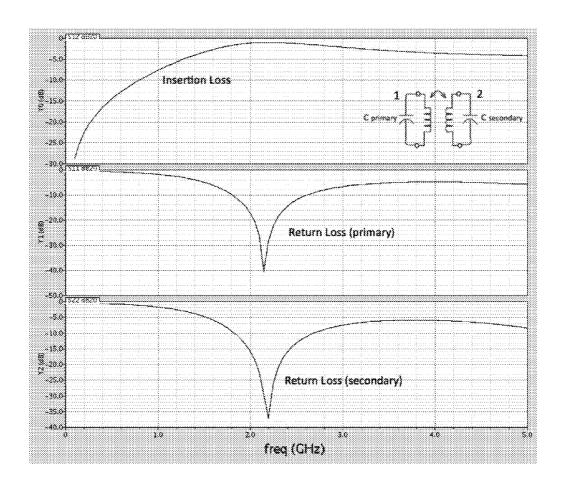

FIG. 3 illustrates electrical performance of a tuned trans-

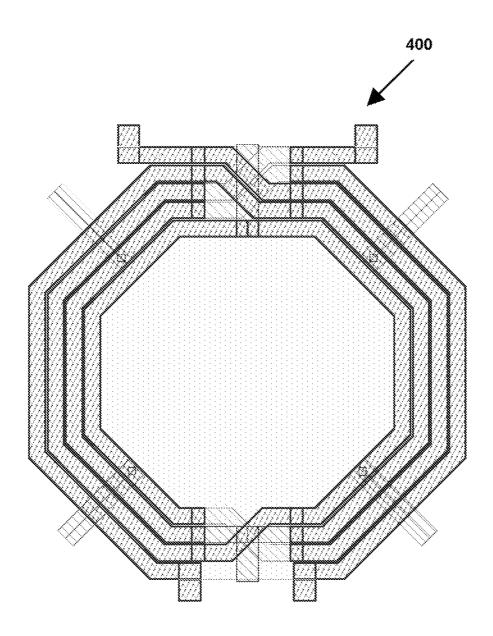

FIG. 4 illustrates a layout of a multi-tap transformer.

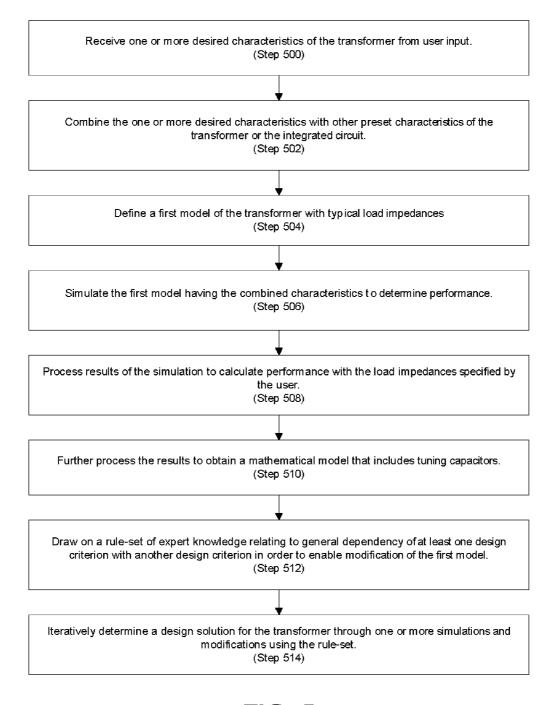

FIG. 5 is a flowchart of an embodiment of a method for designing a transformer in an integrated circuit in accordance with the present invention.

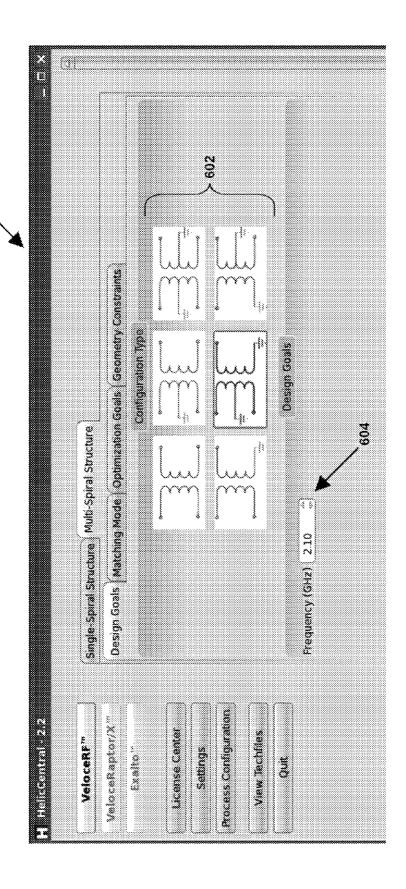

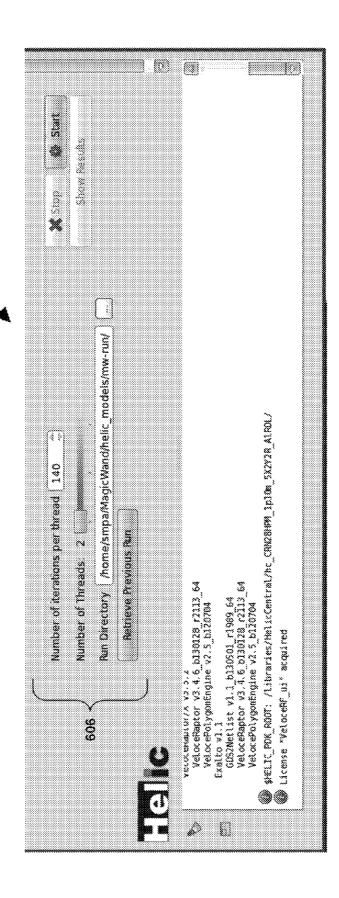

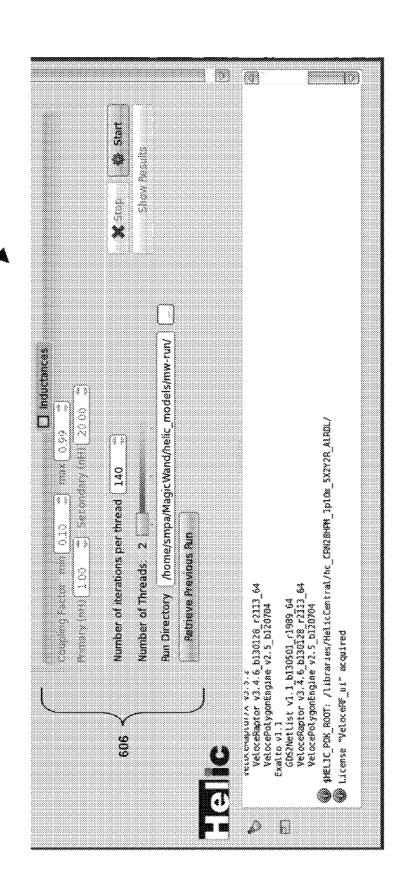

FIGS. 6A and 6B illustrate an embodiment of a user interface for selecting a transformer configuration and center frequency in accordance with the present invention.

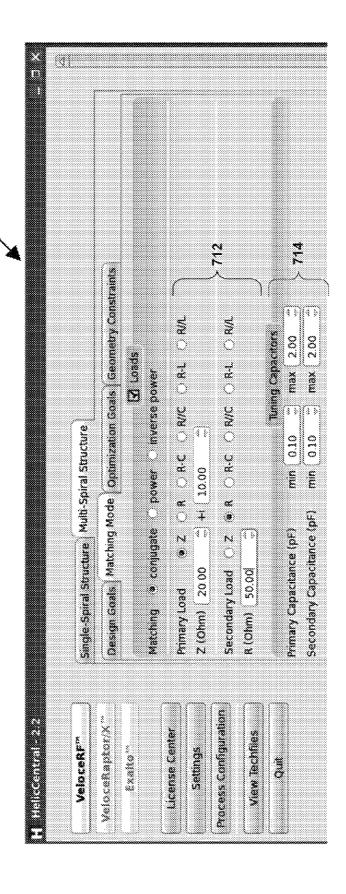

FIGS. 7A and 7B illustrate an embodiment of a form for defining impedance matching properties, load specifications, and tuning capacitor ranges when designing an IC including a transformer in accordance with the present invention.

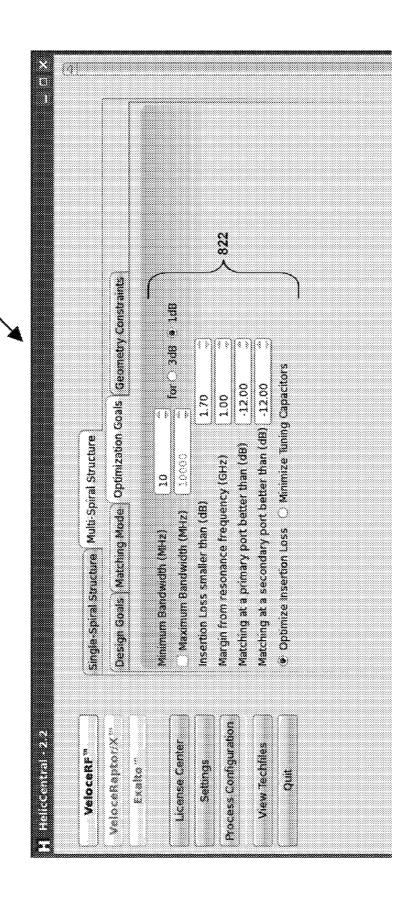

FIGS. 8A and 8B illustrate is an embodiment of a form for entering bandwidth, insertion and return loss constraints when designing an IC including a transformer in accordance with the present invention.

FIGS. 9A and 9B illustrate is an embodiment of contains a form for defining layout geometry options and size con-

straints when designing an IC including a transformer in accordance with the present invention.

#### DETAILED DESCRIPTION

As disclosed in U.S. application Ser. No. 12/575,410 entitled "EXPERT SYSTEM BASED INTEGRATED INDUCTOR SYNTHESIS AND OPTIMIZATION" by Bantas et al., incorporated herein by reference, the physical design of an integrated electrical component such as a spiral 10 inductor can be effectively determined using a computer implemented method. The disclosed method iteratively uses electrical circuit simulation to determine the performance of a candidate physical component and draws on a rule-set of expert knowledge to enable modification of its physical 15 properties, until a set of user-provided objectives and constraints are met. The model of a candidate physical design is preferably provided by an efficient electromagnetics (EM) model extraction engine. The disclosed method brings several advantages such as rapid execution and a high degree of 20 computer-assisted automation; it has been incorporated in the VeloceRFTM EDA product offered by Helic, Inc. and is being used by several semiconductor design companies in production.

Having efficiently resolved the problem of designing 25 integrated components such as spiral inductors, in the invention disclosed herein we concentrate on the related problem of designing integrated transformers.

Referring to FIGS. 2A-2E, several transformer configurations can be defined, depending on the signal conditions at 30 the primary and secondary coils, and the existence of a center tap on either coil or the absence thereof. The configurations are as follows:

- A. Differential to differential.

- B. Differential with center tap, to differential.

- C. Differential with center tap, to differential with center tap.

- D. Differential to single-ended, sometimes referred-to as a 'balun'.

- E. Differential with center tap, to single-ended.

The problem of optimally designing an integrated transformer presents some difficulties, which are known to those skilled in the art, such as:

On substrates such as silicon, the transformation ratio of, for instance, a "1:1" spiral transformer is far from unity. 45 Electromagnetic modeling of transformer layout and simulation of this model with the actual loads presented to the transformer, are needed to determine performance. These steps are typically time-consuming and several iterations may be needed to achieve an optimal 50 design.

Besides the transformer (coil) geometry, for practical design capacitors may need to be designed coupled to the primary and/or secondary coils, for achieving a tuned LC circuit along with the inductance of the coils, 55 which helps to minimize insertion loss, an unwanted side-effect. The performance of a tuned transformer, in terms of S-parameter responses, is illustrated in FIG. 3. The size of these capacitors should be designed in conjunction with the transformer itself, thereby increasing the number of potential design iterations.

The actual load specifications on at least one of the primary or secondary coils may not be known in advance, as these vary greatly depending on the sizing of the transistors and other components of the integrated circuitry that connects to the transformer. Ideally, the transformer block should be co-designed in

4

iteration with the active circuit, e.g. the power amplifier (PA), which may not be practical due to time constraints

The method and apparatus disclosed in U.S. application 5 Ser. No. 12/575,410 helps to overcome some of the limitations described above. However, these need to be adapted and extended for tackling the problem of integrated transformers. The additional steps necessary are disclosed herein.

As disclosed in U.S. application Ser. No. 12/575,410, an expert system-based inductor synthesis system can comprise the following modules:

- a Model Extraction Engine, which creates a model for an under-test candidate spiral geometry;

- a Simulator, which simulates the model and measures the parameters needed by the expert system;

- a rule set, which encapsulates expert knowledge for processing the information received from simulations and inferring the next candidate geometry that should be tested:

components of a software-based expert system, such as an Inference Engine; and

preferably, a user interface for communicating with the

Specific functions need to be introduced at the Model Extraction and Simulation steps to enable optimal transformer design according to this invention.

We first define a set of formulae that are used in the invention:

Scattering parameters (S-parameters)

Let T be a given transformer instance. By performing S-parameter analysis for a set of M frequencies:

$$F=\{f(1),\ldots f(M)\}$$

35

we obtain a set s of S-parameter matrices:

$$s(i) = \begin{vmatrix} s_{11}(i) & s_{12}(i) \\ s_{21}(i) & s_{22}(i) \end{vmatrix}$$

for each i in  $\{1, \ldots, M\}$ .

Impedance Matrix

For any given S-parameter matrix S(i), we can obtain the corresponding impedance matrix,

$$z(i) = \begin{vmatrix} z_{11}(i) & z_{12}(i) \\ z_{21}(i) & z_{22}(i) \end{vmatrix}$$

from the known formulae (as taught in "S-Parameter Techniques", Application Note 95-1, by Agilent Technologies, incorporated herein by reference):

$$Z11=Z0\cdot((1+S11)\cdot(1-S22)+S12\cdot S21)/\det(I-S)$$

$Z12=Z0\cdot 2\cdot S12/\det(I-S)$

$Z21=Z0\cdot 2\cdot S21/\det(I-S)$

$$Z22=Z0\cdot((1-S11)\cdot(1+S22)+S12\cdot S21)/\det(I-S)$$

where z0 the characteristic impedance (e.g. 50 Ohm). Inductance

If z(i) represents the impedance matrix of a transformer, the primary and secondary inductances can be calculated by:

$$L1(i)=Im(Z11(i))/(2 \cdot \pi \cdot f(i))$$

$$L2(i)=Im(Z22(i))/(2\cdot\pi\cdot f(i))$$

5

$$k(i)=Im(Z12(i))/sqrt(Im(Z11(i))\cdot Im(Z22(i)))$$

where index 1 is assumed to correspond to the primary coil port of the transformer, and index 2 to the secondary coil

The resonance frequency Fres of the transformer, such 5 that,

$$f(k) \le Fres \le f(k+1)$$

L1(k)>0 and L2(k)>0

$$L1(k+1) \le 0$$

or  $L2(k+1) \le 0$

can be calculated by linear interpolation, after finding the first value of i for which L1(i)L1(i+1)<0, or L2(i)L2(i+1)<0.

If z(i) represents the impedance matrix of a transformer, the primary and secondary quality factor can be calculated by:

$$QI(i)=Im(Z11(i))/Re(Z11(i))$$

$$Q2(i)=Im(Z22(i))/Re(Z22(i))$$

The maximum quality factor QImax, Q2max and the corresponding frequencies F1max, F2max can also be calculated by evaluating the discrete functions Q1(i), Q2(i) for 25 each sampled frequency  $f(1) \le f(i) \le F(i)$

Bandwidth

We define the bandwidth of a transformer in terms of its insertion loss S12. Let S12\_ref be the insertion loss at a -1 dB or ~3 dB relative to s12\_ref) the bandwidth can then be described as a frequency interval:

$$BW=[f_ref-f_BW1,f_ref+f_BW2]$$

such that:

$S12(f_ref-f_BW1)=S12_ref-S12_tol$

$S12(f_ref+f_BW2)=S12_ref-S12_tol$

and:

S12(f)>S12\_ref-S12\_tol

for all f in BW.

The bandwidth of a transformer at given frequency f(i) 45 can be numerically approximated as follows:

Define  $S12\_ref=S12(i)$  and  $f\_ref=f(i)$ .

Locate the first k>i such that S12(k)<=S12\_ref-S12\_tol and obtain f\_BW2 by linear interpolation between (S12(k-1), f(k-1)) and (S12(k), f(k)).

Locate the last k<i such that S12(k)<=S12\_ref-S12\_tol and obtain f\_BW1 by linear interpolation between (S12(k), f(k)) and (S12(k+1), f(k+1)).

Arbitrary Loads

The S-parameter matrix S(i) is measured with both ports 55 connected to reference loads of Z0=50 ohm. If the circuit is connected to arbitrary complex loads Zp, Zs, its electrical behavior is described by a transformation of S(i) as described in the book "Microwave Amplifiers and Oscillators" by Christian Gentili, incorporated herein by reference: 60

$$s'(i) = \begin{vmatrix} s'_{11}(i) & s'_{12}(i) \\ s'_{21}(i) & s'_{22}(i) \end{vmatrix}$$

where:

6

$$S11'=((1-Gs\cdot S22)\cdot (S11-\operatorname{Conj}(Gp))+S12\cdot S21\cdot Gs\cdot A11)/DS$$

$S12'=(S12\cdot(1.0-|Gp|^2)\cdot A21)/DS$

$$S21' = (S21 \cdot (1.0 - |G_S|^2) \cdot A12)/DS$$

$$S22'=((1-Gp\cdot S11)\cdot (S22-\text{Conj}(Gs))+S12\cdot S21\cdot Gp\cdot A22)/DS$$

10 and where the reflection coefficients are defined as:

$$Gp = (Zp - Z0)/(Zp + Z0)$$

$$Gs = (Zs - Z0)/(Zs + Z0)$$

15 and the remaining matrices are defined as:

$$A = \left[ \begin{array}{cc} A_{11} & A_{12} \\ A_{21} & A_{22} \end{array} \right] = \left| \begin{array}{cc} Conj(Ap)/Ap & Conj(Ap)/As \\ Conj(As)/Ap & Conj(As)/As \end{array} \right]$$

$Ap = ((1 - \text{Conj}(Gp)) \cdot \text{Sqrt}(1.0 - |Gp|^2)))|1 - Gp|$

$$As = ((1-\operatorname{Conj}(Gs))\cdot\operatorname{Sqrt}(1.0-|Gs|^22)))|1-Gs|$$

$$DS = (1 - Gp \cdot S11) \cdot (1 - Gs \cdot S22) - (S12 \cdot S21 \cdot Gp \cdot Gs)$$

Cascaded Circuits

For any given S-parameter matrix s, we can obtain the given frequency f\_ref. Given a tolerance value S12\_tol (e.g. 30 corresponding scattering transfer parameter (T-parameter) matrix (as taught in "S-Parameter Design", Application Note 154, by Agilent Technologies):

$$T = \begin{vmatrix} T_{11} & T_{12} \\ T_{21} & T_{22} \end{vmatrix}$$

using the formulae:

$T11 = -\det(S)/S12$

T12=SII/S12

T21 = -S22/S12

T22=1/S12

Consider a pair of 2-port circuits described by their S-parameter matrices S1 and S2. By definition, the T-parameter matrix T of the cascaded circuit is given by:

$$T=T1 \cdot T2$$

where T1, T2 the T-parameter matrices corresponding to S1 and S2 respectively.

The S-parameter matrix of the cascaded circuit can then be calculated by the reverse transformation:

SII = T12/T22

S12 = det(T)/T22

S21=1/T22

$$S22 = -T21/T22$$

**Tuning Capacitors**

Consider a 2-port network consisting of a shunt capacitor C. The S-parameter matrix of this circuit would be:

$$s_c(C, f) = \begin{vmatrix} -y(C, f) & 2 \\ 2 & -y(C, f) \end{vmatrix} \cdot \frac{1}{y(C, f) + 2}$$

where y(C,f) is the normalized admittance of C and f the frequency, whereby:

$$y(C,f)=j\cdot 2\cdot \pi \cdot f\cdot C$$

The corresponding T-parameter matrix is given by:

$$T_c(C, f) = \begin{vmatrix} 2 - y(C, f) & -y(C, f) \\ y(C, f) & 2 + y(C, f) \end{vmatrix} \cdot \frac{1}{2}$$

Now, consider a transformer described by a set of S-parameter matrices S(i) and a pair of tuning capacitors c1, connected in parallel to port 1 (primary), and c2, connected in parallel to port 2 (secondary).

Then, the T-parameter matrix of the whole (tuned) transformer circuit, for any sampled frequency f(i), is given by:

$$Ttun(cl,c2,i) = Tc(cl,f(i)) \cdot T(i) \cdot Tc(c2,f(i))$$

The S-parameter matrix stun (c1, c2, i) of the tuned 25 transformer can easily be obtained by a simple T-to-S transformation.

Transformer Inductance and Quality Factor Calculation Given a transformer described by:

a set of S-parameter matrices S,

sampled at a set of frequencies  $F = \{f(1), \dots, f(M)\}$ , and an operating frequency f(i), i in  $\{1, \ldots, M\}$ ,

Using the formulae provided above in reference to inductance, we may easily calculate and return the following quantities:

the primary/secondary inductances L1 (i), L2 (i), k(i), the primary/secondary quality factors Q1 (i), Q2(i),

the maximum quality factors (Q1max, F1max), (Q2max, F2max), and

the resonance frequency Fres.

Transformer Optimization to Arbitrary Loads

We next disclose a method according to the invention, for optimizing an instance of a transformer design coupled to arbitrary loads.

Given a transformer described by:

a set of S-parameter matrices s.

sampled at a set of frequencies  $F = \{f(1), \dots, f(M)\}$ , and given an operating frequency f(i), with i in  $\{1, \ldots, m\}$

defined either as fixed complex numbers or as RL/RC series/parallel circuits, we calculate a pair of tuning capacitors c1, c2 such that the insertion loss S12'(i) of the tuned circuit is maximal, subject to the following constraints:

the capacitor values are restricted by

c1 in [c1min, c1max], and

c2 in [c2min, c2max].

the return losses are restricted by

$S11' \le RL_max$ , and

S22'<=RL max.

the bandwidth  $[f(i)-f_BW1, f(i)+f_BW2]$  of S12' is restricted by

f BW1>=BW min, and

f BW2<=BW max.

The above equations define a bounded constrained optimization problem, which is solvable by known methods, such as Powell's COBYLA (Constrained Optimization BY Linear Approximations) algorithm for derivative-free optimization with nonlinear inequality constraints, which is described in the paper by M. J. D. Powell, "A direct search optimization method that models the objective and constraint functions by linear interpolation", Advances in Optimization and Numerical Analysis, 1994, p. 51-67, incorporated herein by reference.

The COBYLA method constructs linear approximations 10 to the objective and the constraint functions by interpolating between the vertices of a n-dimensional simplex, where n the number of variables (in this case, the variables being c1 and c2, we have n=2).

We then define, according to the invention, a callback 15 function callback(c1, c2) which performs the following operations:

obtains reference S-parameter matrix S;

for each frequency f(i) in F:

performs T-parameter cascade transformation (as described above in reference to cascaded circuits) to calculate the S-parameter matrix S\_cap of the tuned transformer circuit with reference loads, according to a desired transformer configuration,

performs arbitrary load conversion (as described in reference to arbitrary loads) on S cap to obtain the S-parameter matrix S\_tuned of the tuned transformer circuit with loads Zp, Zs,

performs bandwidth calculation (as described in reference to bandwidth) on S\_tuned to obtain the bandwidth f\_BW1, f\_BW2, and

calculates the objective function |S12\_tuned(i)|, i.e. the insertion loss at the operating frequency f(i).

Calculates the constraints:

err\_c1, proportional to

c1-c1min if c1min>c1, or

c1max-c1 otherwise.

err\_c2, proportional to

c2-c2min if c2min>c2, or

c2max-c2 otherwise.

40

60

err\_rl1, proportional to RL\_max-SII.

Err\_rl2, proportional to RL\_max-S22.

err\_bw1, proportional to f\_BW1-BW\_min.

err\_bw2, proportional to BW\_max-f\_BW2.

The COBYLA optimization engine calls callback(cl, c2) 45 repeatedly for various values of c1, c2, attempting to

minimize the objective value, and

make all constraints nonnegative.

The invention can be adapted by those skilled in the art, to incorporate alternative constrained optimization methods, a pair of primary/secondary loads Zp, Zs, which may be 50 equivalent to COBYLA and/or alternative constraints to meet the desired objectives.

Although the invention is presented here with embodiments involving transformers with primary and secondary coils, and with optional taps at either primary and/or sec-55 ondary coils connected at fixed potential, those skilled in the art will realize that it can be extended and applied to the synthesis and optimization of 'multi-tap' transformers 400 as well (illustrated in FIG. 4), whereby each of a plurality of taps may be connected to a signal at a given impedance level.

The above constrained optimization problem may be combined with a simulation based expert system method to accomplish physical design synthesis and optimization of transformers, including the design of tuning capacitors, in an advantageous manner. Those skilled in the art will appreciate upon reflecting on the teaching included herein that an EDA method thus implemented will automate the process of

implementing integrated transformers and will moreover provide a valuable tool to circuit designers for optimizing their circuits employing transformers.

Referring to FIG. 5, a flowchart of an embodiment of a method for designing a transformer in an integrated circuit 5 in accordance with the present invention is shown. The method comprises iteratively determining a design solution for the transform through one or more simulations and modification using a rule set. The method further comprises receiving one or more desired characteristics of the transformer from user input (Step 500). The one or more desired characteristics are combined with other preset characteristics of the transformer or the integrated circuit (Step 502). A first model of the transformer is defined with typical load impedances (Step 504). The first model is simulated having 15 the combined characteristics to determine performance of the first model (Step 506). Results of the simulation are then processed to calculate performance with the load impedances specified by the user (Step 508). The results are further processed to obtain a mathematical model that includes 20 tuning capacitors (Step 510). The design solution is then iteratively determined drawing on a rule set of expert knowledge relating to generate dependency of the at least one design criterion, such as a physical, geometrical or performance characteristic, with another design criterion in 25 order to enable modification of the first model and subsequent iterative models (Steps 512 and 514).

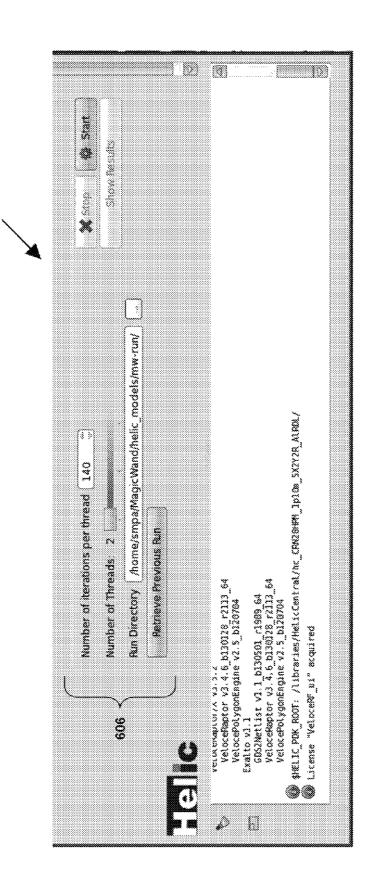

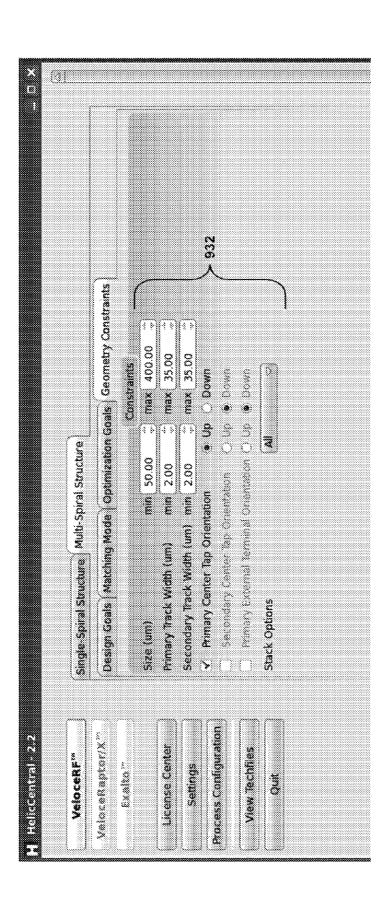

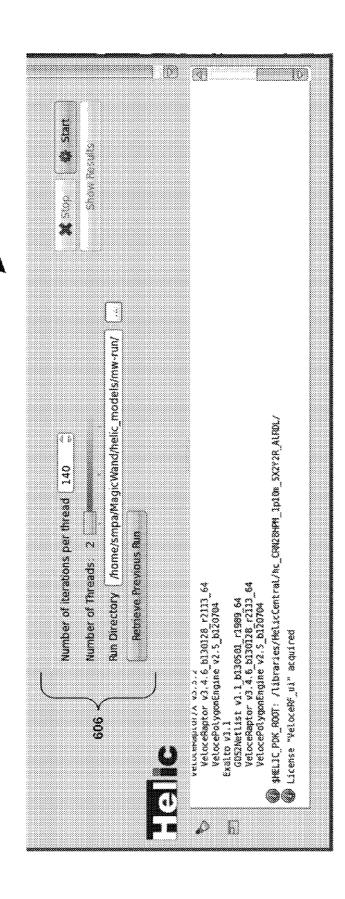

To further enhance the usefulness of the invention, we propose a user interface whereby circuit designers may enter their desired parameters and accomplish automated trans- 30 former synthesis and optimization. Such parameters may include electrical specifications for the transformation, geometrical constraints for the transformer's physical layout, and other parameters, objectives and constraints that are relevant to the circuit being designed. FIGS. 6A and 6B 35 illustrate a form 600 with a design goals tab selected for defining the transformer configuration, defined by selecting the configuration in the configuration type frame 602, and center frequency, defined in the frequency selection frame 604. FIGS. 7A and 7B illustrate the form 600 with a 40 matching mode tab selected for defining the impedance matching properties and load specifications, defined in a load settings frame 712, and tuning capacitor ranges, defined in the capacitance selection frame 714. FIGS. 8A and 8B illustrate the form 600 with an optimization goals tab 45 selected for defining bandwidth, insertion and return loss constraints, each defined in the optimization goals frame 822. FIGS. 9A and 9B illustrate the form 600 with a geometry constraints menu selected for defining layout geometry options and size constraints, defined in the geom- 50 etry constraints menu 932. The form 600 further includes an iteration selection frame 606 for defining a number of iteration a simulation should perform. The method can further include receiving one or more optimization targets and solving a constrained optimization problem to determine 55 optimal values of the tuning capacitors based on the one or more desired characteristics and the one or more optimization targets.

The present invention may be conveniently implemented using one or more conventional general purpose or specialized digital computer, computing device, machine, or microprocessor, including one or more processors, memory and/or computer readable storage media programmed according to the teachings of the present disclosure. Appropriate software coding can readily be prepared by skilled programmers 65 based on the teachings of the present disclosure, as will be apparent to those skilled in the software art.

10

In some embodiments, the present invention includes a computer program product which is a storage medium or computer readable medium (media) having instructions stored thereon/in which can be used to program a computer to perform any of the processes of the present invention. The storage medium can include, but is not limited to, any type of disk including floppy disks, optical discs, DVD, CD-ROMs, microdrive, and magneto-optical disks, ROMs, RAMs, EPROMs, EEPROMs, DRAMs, VRAMs, flash memory devices, magnetic or optical cards, nanosystems (including molecular memory ICs), or any type of media or device suitable for storing instructions and/or data.

The previous description of the preferred embodiments is provided to enable any person skilled in the art to make or use the embodiments of the present invention. While the invention has been particularly shown and described with reference to preferred embodiments thereof, it will be understood by those skilled in the art that various changes in form and details may be made therein without departing from the spirit and scope of the invention.

What is claimed is:

- 1. An apparatus for designing a transformer in an integrated circuit, the apparatus comprising:

- a processor;

- a user interface adapted to allow a user to input one or more desired characteristics of the transformer;

- wherein the one or more desired characteristics include load impedances at primary and secondary coils of the transformer;

- wherein the processor is configured to determine sufficient optimal characteristics of the transformer to define the transformer for fabrication in the integrated circuit by performing the steps of:

- combining the one or more desired characteristics with other preset characteristics of the transformer or the integrated circuit,

- generating a first model of the transformer with typical load impedances,

- simulating the first model having the combined characteristics to determine performance,

- processing results of the simulation to calculate performance with the load impedances specified by the user,

- further processing the results to generate a mathematical model that includes tuning capacitors coupled to primary or secondary coils of the transformer to achieve a tuned LC circuit with the inductance of the transformer coils,

- drawing on a rule-set of one or more rules relating to general dependency of at least one design criterion on another design criterion, the design criteria relating to one or more of physical, geometrical or performance characteristics to enable modification of the first model, and

- iteratively determining a design solution for the transformer through one or more simulations and modifications using the rule-set,

- wherein the user interface is adapted to allow a user to input one or more optimization targets, and

- wherein the processor further performs the steps of:

- solving a constrained optimization problem to determine optimal values of the tuning capacitors based on the one or more desired characteristics and the one or more optimization targets.

- 2. The apparatus of claim 1, wherein the user interface is adapted to allow a user to input one or more optimization targets; and

11

- wherein the processor further performs the steps of solving a constrained optimization problem to determine optimal values of the tuning capacitors based on the one or more desired characteristics and the one or more optimization targets.

- 3. The apparatus of claim 2, wherein the one or more optimization targets include lowest possible insertion loss.

- **4**. The apparatus of claim **1**, wherein the transformer includes a plurality of taps connecting the primary coil to either a fixed potential, a signal, or a load.

- 5. The apparatus of claim 1, wherein the transformer includes a plurality of taps connecting the secondary coil to either a fixed potential, a signal, or a load.

- **6.** A method for designing a transformer in an integrated circuit, the method comprising:

- receiving one or more desired characteristics of the transformer from user input;

- combining the one or more desired characteristics with other preset characteristics of the transformer or the integrated circuit;

- generating a first model of the transformer with typical load impedances;

- simulating the first model having the combined characteristics to determine performance;

- processing results of the simulation to calculate perfor- 25 mance with the load impedances specified by the user;

- further processing the results to generate a mathematical model that includes tuning capacitors coupled to primary or secondary coils of the transformer to achieve a tuned LC circuit with the inductance of the transformer coils;

- drawing on a rule-set of one or more rules relating to general dependency of at least one design criterion on another design criterion, the design criteria relating to one or more of physical, geometrical or performance 35 characteristics to enable modification of the first model; and

- iteratively determining a design solution for the transformer through one or more simulations and modifications using the rule-set,

- wherein the user interface is adapted to allow a user to input one or more optimization targets; and

- wherein a processor further performs the steps of

- solving a constrained optimization problem to determine optimal values of the tuning capacitors based on the 45 one or more desired characteristics and the one or more optimization targets.

- 7. The method of claim 6, further comprising:

- receiving one or more optimization targets from user input; and

- solving a constrained optimization problem to determine optimal values of the tuning capacitors based on the one or more desired characteristics and the one or more optimization targets.

- **8**. The method of claim **7**, wherein the one or more 55 optimization targets include lowest possible insertion loss.

- **9**. The method of claim **6**, wherein the transformer includes a plurality of taps connecting the primary coil to either a fixed potential, a signal, or a load.

12

- 10. The method of claim 6, wherein the transformer includes a plurality of taps connecting the secondary coil to either a fixed potential, a signal, or a load.

- 11. A non-transitory machine readable medium having instructions thereon that when executed by a processor cause an apparatus to:

- receive one or more desired characteristics of a transformer from user input;

- combine the one or more desired characteristics with other preset characteristics of the transformer or an integrated circuit of which the transformer is a component;

- generate a first model of the transformer with typical load impedances;

- simulate the first model having the combined characteristics to determine performance; process results of the simulation to calculate performance with the load impedances specified by the user;

- further process the results to generate a mathematical model that includes tuning capacitors coupled to primary or secondary coils of the transformer to achieve a tuned LC circuit with the inductance of the transformer coils;

- draw on a rule-set of one or more rules relating to general dependency of at least one design criterion on another design criterion, the design criteria relating to one or more of physical, geometrical or performance characteristics to enable modification of the first model; and iteratively determine a design solution for the transformer through one or more simulations and modifications using the rule-set,

- wherein the user interface is adapted to allow a user to input one or more optimization targets; and

- wherein the processor further performs the steps of

- solving a constrained optimization problem to determine optimal values of the tuning capacitors based on the one or more desired characteristics and the one or more optimization targets.

- 12. The non-transitory machine readable medium of claim 11, further comprising instructions thereon that when executed cause an apparatus to:

- receive one or more optimization targets from user input; and

- solve a constrained optimization problem to determine optimal values of the tuning capacitors based on the one or more desired characteristics and the one or more optimization targets.

- 13. The method of claim 12, wherein the one or more optimization targets include lowest possible insertion loss.

- 14. The non-transitory machine readable medium of claim 12, wherein the transformer includes a plurality of taps connecting the primary coil to either a fixed potential, a signal, or a load.

- 15. The non-transitory machine readable medium of claim 12, wherein the transformer includes a plurality of taps connecting the secondary coil to either a fixed potential, a signal, or a load.

\* \* \* \* \*